# Freescale Semiconductor Reference Manual Errata

MCF5213RMAD Rev. 5, 11/2011

# MCF5213 Reference Manual Errata

Supported Devices: MCF5211, MCF5212, MCF5213

by: Microcontroller Solutions Group

This errata document describes corrections to the *MCF5213 Reference Manual*, order number MCF5213RM. For convenience, the addenda items are grouped by revision. Please check our website at <a href="http://www.freescale.com/coldfire">http://www.freescale.com/coldfire</a> for the latest updates.

The current available version of the *MCF5213 Reference Manual* is Revision 5.

#### **Contents**

| 1 | Errata for Revision 5 | 2 |

|---|-----------------------|---|

|   | Errata for Revision 3 |   |

| 3 | Errata for Revision 2 | 6 |

| 4 | Revision History      | 8 |

**Errata for Revision 5**

### 1 Errata for Revision 5

Table 1. MCF5213RMAD Reference Manual Rev 5 Errata

#### Table 1. MCF5213RMAD Reference Manual Rev 5 Errata (continued)

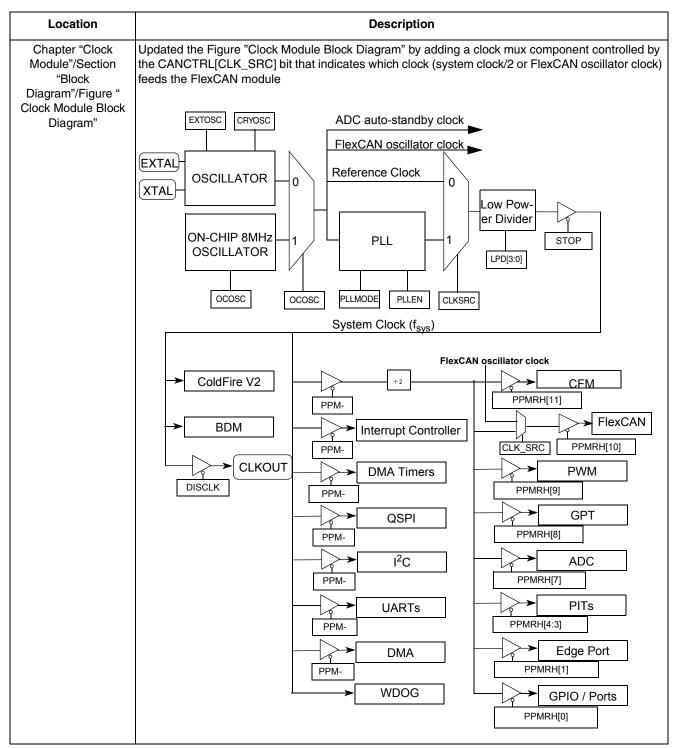

| Location                                                                                           | Description                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter "FlexCAN" Section "FlexCAN Control Register (CANCTRL)" /Table "CANCTRL Field Descriptions" | Change from: $S \ clock \ frequency = \frac{f_{SVS} \ or \ EXTAL}{PRESDIV + 1}$ Change to: $S \ clock \ frequency = \frac{f_{SVS/2} \ or \ FlexCAN \ oscillator \ clock}{PRESDIV + 1}$                                                  |

| Chapter "FlexCAN" Section "FlexCAN Control Register (CANCTRL)" /Table "CANCTRL Field Descriptions" | In the Description of field 13 CLK_SRC bit Change from:  0 Clock source is EXTAL 1 Clock source is the internal bus clock, fsys Change to:  0 Clock source is FlexCAN oscillator clock 1 Clock source is the internal bus clock, fsys/2 |

| Chapter "FlexCAN"<br>/Section "Protocol<br>Timing"/Figure "CAN<br>Engine Clocking<br>Scheme"       | Change from: $f_{Tq}=\frac{f_{\rm sys}~{\rm or}~{\rm EXTAL}}{({\rm PRESDIV}+1)}$ Change to: $f_{Tq}=\frac{f_{\rm sys/2}~{\rm or}~{\rm FlexCAN}~{\rm oscillator}~{\rm clock}}{{\rm PRESDIV}+1}$                                          |

#### **Errata for Revision 3**

# 2 Errata for Revision 3

#### Table 2. MCF5213RM Rev 3 Errata

| Location                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 1.4, "Features"/Page 7  | <ul> <li>In clock generation features:</li> <li>Replaced "One to 48 MHz crystal, 8 MHz on-chip trimmed relaxation oscillator, or external oscillator reference options" with "Crystal, on-chip relaxation oscillator, or external oscillator reference options".</li> <li>Updated "Two to 10 MHz reference frequency for normal PLL mode with a pre-divider programmable from 1 to 8" with "Two to 10 MHz reference frequency for normal PLL mode".</li> </ul> |

| Section 6.2, "Features"/Page 81 | Replaced "1- to 16-MHz crystal, 8-MHz on-chip relaxation oscillator, or external oscillator reference options" with "Crystal, on-chip relaxation oscillator, or external oscillator reference options."                                                                                                                                                                                                                                                        |

| Throughout                      | Formatting, layout, spelling, and grammar corrections.                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 2-1 / Page 2-3            | Synchronized the table in the reference manual and the device data sheet.                                                                                                                                                                                                                                                                                                                                                                                      |

| Section 10.5.4 / Page 10-7      | Updated the section to reflect the fact that the CWT does not cause a hardware reset.                                                                                                                                                                                                                                                                                                                                                                          |

| Table 10-6 / Page 10-8          | In the CWCR[CWRI] field description, changed "The interrupt level for the CWT is programmed in the interrupt control register 7 (ICR7)" to "The interrupt level for the CWT is programmed in the interrupt control register 8 (ICR8)".                                                                                                                                                                                                                         |

| Section 12-1 / Page 12-2        | Deleted the sentence beginning with "For many peripheral devices".                                                                                                                                                                                                                                                                                                                                                                                             |

| Table 12-2 / Page 12-5          | Deleted the entry for the (nonexistent) GSWIACK register.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Section 12.3.8 / Page 12-16     | Deleted references to the (nonexistent) GSWIACK register.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Section 14.4 / Page 14-12       | Deleted the sentence "BCR $n$ decrements when an address transfer write completes for a single-address access (DCR $n$ [SAA] = 0), or when SAA equals 1."                                                                                                                                                                                                                                                                                                      |

| Section 10.7.3.1 / Page 10-14   | <ul> <li>Rewrote the introductory text describing the MPR (removing erroneous reference to a fast Ethernet controller).</li> <li>Corrected the MPR reset value (was 0x11, is 0x1).</li> </ul>                                                                                                                                                                                                                                                                  |

| Figure 21-6 / Page 21-9         | Added a note to clarify the UCSRn reset values.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 21-20 / Page 21-20       | <ul> <li>Corrected the label of the top signal (was UnTXD, is UnRXD).</li> <li>Corrected the text in the footnote (was TXRTS, is RXRTS).</li> </ul>                                                                                                                                                                                                                                                                                                            |

| Figure 21-23 / Page 21-23       | Corrected the UnTXD label (was "Input", is "Output").                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 21-24 / Page 21-24       | <ul> <li>Corrected a label on the bottom row (was UMR1n[PT]=2, is UMR1n[PT]=1).</li> <li>Deleted duplicate UMR1n[PM]=11 label.</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| Section 24.3.2.5.1 / Page 24-17 | Corrected the numerical values in the left-aligned example.                                                                                                                                                                                                                                                                                                                                                                                                    |

| Section 24.3.2.6.1 / Page 24-19 | Corrected the numerical values in the center-aligned example.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Appendix A                      | Deleted the entry for the (nonexistent) GSWIACK register.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Throughout                      | Formatting, layout, spelling, and grammar corrections.                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 1-1 / Page 1-2            | Added the following footnote to the MCF5211 FlexCAN entry: "FlexCAN is available on the MCF5211 only in the 64 QFN package."                                                                                                                                                                                                                                                                                                                                   |

| Table 2-1 / Page 2-3            | Changed the value in the "Pull-up/pull-down" column for IRQ2-IRQ6 (was "—", is "pull-up").                                                                                                                                                                                                                                                                                                                                                                     |

#### Table 2. MCF5213RM Rev 3 Errata (continued)

| Location                      | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3-1 / Page 3-3          | <ul> <li>For the PC, changed the reset value (was "Undefined", is "Contents of Location 0x0000_0004") and the "Written with MOVEC entry" value (was "Yes", is "No").</li> <li>Changed the reset value for the OTHER_A7 (was "Undefined", is "Contents of Location 0x0000_0000").</li> <li>Changed the reset value for the RAMBAR (was "0x0000_0000", is "See Section").</li> </ul>                                    |

| Figure 3-5 / Page 3-5         | <ul> <li>Modified the figure to show that Bits 4:0 are read/write.</li> <li>Changed the access (was "Access: User read-only", is "Access: User read/write").</li> </ul>                                                                                                                                                                                                                                               |

| Table 3-2 / Page 3-6          | Removed the last sentence in the C bit field description.                                                                                                                                                                                                                                                                                                                                                             |

| Figure 3-7 / Page 3-6         | Updated the figure to show that bits 19:0 are read-only.                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3-8 / Page 3-7         | Updated the figure to show that bits 4:0 are read/write.                                                                                                                                                                                                                                                                                                                                                              |

| Section 3.4 / Page 3-9        | Changed the last sentence in step 2 to "The IACK cycle is mapped to special locations within the interrupt controller's address space with the interrupt level encoded in the address".                                                                                                                                                                                                                               |

| Table 5-1 / Page 5-2          | Changed the RAMBAR reset value (was "0x0000_0000", is "See Section").                                                                                                                                                                                                                                                                                                                                                 |

| Section 5.2.1 / Page 5-2      | Corrected section to show the proper RAMBAR figure and field description table.     Changed the last bullet to "A reset clears the RAMBAR's priority, backdoor write-protect, and valid bits, and sets the backdoor enable bit. This enables the backdoor port and invalidates the processor port to the SRAM. (The RAMBAR must be initialized before the core can access the SRAM.) All other bits are unaffected.". |

| Table 7-2 / Page 7-2          | Deleted superfluous table.                                                                                                                                                                                                                                                                                                                                                                                            |

| Section 7.2.4.1 / Page 7-9    | <ul> <li>Updated LPCR figure and field description table to include correct information about the STPMD (bits 4:3) and LVDSE (bit 1) fields.</li> <li>Corrected section number (was fourth-level heading, is third-level heading).</li> </ul>                                                                                                                                                                         |

| Table 8-3 / Page 8-3          | Updated the CIR memory map entry to show that the CIR reset value is device-dependent.                                                                                                                                                                                                                                                                                                                                |

| Figure 8-3 / Page 8-4         | Added a footnote to clarify that the CIR reset value is device-dependent.                                                                                                                                                                                                                                                                                                                                             |

| Table 10-1 / Page 10-2        | Added missing PACRn addresses.                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 10-4 / Page 10-7       | Corrected name of bit 0 (was CWTIC, is CWTIF).                                                                                                                                                                                                                                                                                                                                                                        |

| Table 10-12 / Page 10-15      | Added an entry for PACR5 and a footnote to clarify the meaning of "—".                                                                                                                                                                                                                                                                                                                                                |

| Table 14-4 / Page 14-8        | Deleted erroneous reference to nonexistent AT bit.                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 15-3 / Page 15-5       | Updated the FLASHBAR figure to show that WP is read-only, and added footnote to explain that the value of WP is determined at power-on reset.                                                                                                                                                                                                                                                                         |

| Section 18.6.13 / Page 18-12  | Deleted erroneous references to nonexistent CF bits in the figure and bit descriptions for the GPTFLG2 register.                                                                                                                                                                                                                                                                                                      |

| Figure 20-1 / Page 20-1       | Corrected signal name (was QSPI_CS[:0], is QSPI_CS[3:0]).                                                                                                                                                                                                                                                                                                                                                             |

| Section 21.2 / Page 21-3      | Changed "An internal interrupt request signal notifies the interrupt controller" to "A request signal is provided to notify the interrupt controller".                                                                                                                                                                                                                                                                |

| Table 21-6 / Page 21-9        | Changed "DTIN" to "DTnIN" (to maintain consistent signal names throughout chapter).                                                                                                                                                                                                                                                                                                                                   |

| Section 21.4.5.2 / Page 21-26 | Changed "complete normally without exception processing" to "complete normally without an error termination".                                                                                                                                                                                                                                                                                                         |

#### **Errata for Revision 2**

#### Table 2. MCF5213RM Rev 3 Errata (continued)

| Location                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chapter 23                      | <ul> <li>Reorganized information throughout entire chapter.</li> <li>Converted register field descriptions to SRS format.</li> <li>Corrected register mnemonics as necessary to ensure consistent register naming.</li> <li>Numerous grammar and stylistic corrections.</li> </ul>                                                                                                                                                                                                                        |  |

| Chapter 24                      | Updated chapter to reflect the correct number of PWM channels (was 4, is 8).                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Section 24.3.2.5.1 / Page 24-17 | Added missing numerical values to the output example.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Section 24.3.2.6.1 / Page 24-19 | Added missing numerical values to the output example.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Table 24-1 / Page 24-2          | Deleted reference to nonexistent SCMISR register from footnote 2.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Table 26-4 / Page 26-6          | Changed the reset values for PBR1, PBR2, and PBR3 (was "Undefined", is "See Section").                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Table 26-10 / Page 26-16        | <ul> <li>Added the following note to the PBR0[Address] field description:</li> <li>Note: PBR0[0] should always be loaded with a 0.</li> <li>Changed the bit range in the Field column (was 31–1, is 31–0).</li> </ul>                                                                                                                                                                                                                                                                                     |  |

| Figure 26-8 / Page 26-16        | Changed the address of PBR3 (was 0x1C, is 0x1B).                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Table 26-22 / Page 26-38        | Changed the initial state of the CSR (was 0x0, is 0x0090_0000).                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Section 26.6.2 / Page 26-42     | Added the following note at the end of this section:  The debug module requires the use of the internal bus to perform BDM commands. For this processor core, if the processor is executing a tight loop that is contained within a single aligned longword, the processor may never grant the internal bus to the debug module, for example:  align4  label1: nop  bra.b label1  or  align4  label2: bra.w label2  The processor grants the internal bus if these loops are forced across two longwords. |  |

| Figure 27-3 / Page 27-5         | Updated the IDCODE register figure to indicate that the reset values for both PRN and PIN are device-dependent.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Appendix A                      | Corrected PACRn addresses.     Added CFMCLKSEL register.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

# 3 Errata for Revision 2

#### Table 3. MCF5213RM Rev 2 Errata

| Location                 | Description                                                                    |

|--------------------------|--------------------------------------------------------------------------------|

| Throughout               | Formatting, layout, spelling, and grammar corrections.                         |

| Figure 1-1 / Page 1-3    | Corrected signal names to match those in Table 1 in Chapter 2.                 |

| Figure 2-1 / Page 2-2    | Corrected signal names to match those in Table 1.                              |

| Table 1 / Section 2.2    | Changed label to Table 2-1.     Added overbars to names of active-low signals. |

| Section 3.2.9 / Page 3-7 | Added cross-reference to FLASHBAR register.                                    |

MCF5213 Reference Manual Errata, Rev. 5

#### Table 3. MCF5213RM Rev 2 Errata (continued)

| Location                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 3.4 / Page 3-9      | <ul> <li>Changed the last bullet to "Use of separate system stack pointers for user and supervisor modes".</li> <li>Deleted the sentences beginning with "Processors implementing ISA_A" and "As a result, the exception stack frame".</li> <li>Deleted the text "For processors implementing all other ISA revisions and supporting 2 stack pointers".</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Section 3.6.2 / Page 3-12   | Added text clarifying address errors occurring on JSR and RTS instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 4                   | Content updates and enhancements throughout chapter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 5.1.1 / Page 5-1    | Corrected SRAM size.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 5.1.2 / Page 5-1    | Removed text "within the 256-MByte address space (0x8000_0000-0x8FFF_FFFF)".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table 5-2 / Page 5-2        | Removed text "within the processor's 256-MByte address space" and "For proper operation, the base address must be set to between 0x8000_0000 and 0x8FFF-8C000.".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Table 6-6 / Page 6-7        | Added footnote 3 - "Default value out of reset" - to reflect correct reset values of MFD (0b001) and RFD (0b000).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 10-8 / Page 10-13    | Marked bits 17-16 as reserved to match the correct description in Table 10-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Chapter 11                  | <ul> <li>Corrected register addresses to include proper offset (IPSBAR+0x10).</li> <li>Updated register figures to SRS standards.</li> <li>Added descriptive register figure titles and field description tables.</li> <li>Corrected register mnemonics for the Port <i>n</i> pin data/set data registers.</li> <li>Replaced incorrect Figure 11-25 with correct version (containing only PxPAR1 and PxPAR0).</li> <li>In section 11.6.5, changed "If multiple pins are configured for the one function, then the rsult is undefined" to "Some signals can be assigned to different pins (see Table 2-1). However, a signal should not be assigned to more than one pin at the same time. If a signal is assigned to two or more pins simultaneously, the result is undefined."</li> </ul> |

| Chapter 14                  | <ul> <li>Revised Table 14-1 to reflect the structure of the BCRn and DSRn registers.</li> <li>Updated register figures to include proper register names and addresses.</li> <li>Combined Sections 14.3.4 and 14.3.4.1, and revised text to clarify the structure of the BCRn and DSRn registers.</li> <li>Added missing figure and bit descriptions for the DCRn registers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 15                  | Updated register figures to include correct register addresses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Section 15.3 / Page 15-4    | Added definition and description of FLASHBAR register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 18-3 / Page 18-5      | Deleted entry for nonexistent GPTTST register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 18-21                | Updated figure appearance to match document convention.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 21-6 / Page 21-8     | Updated figure with correct register mnemonics (USR02).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Equation 21-1 / Page 21-19  | Corrected numerator of equation (was f <sub>sys/2</sub> , is f <sub>sys</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 23                  | Deleted superfluous Table 23-5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Section 23.5.7 / Page 23-32 | Deleted extraneous sentence at end of first paragraph.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 25                  | Corrected register addresses throughout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 25-9 / Page 25-14    | Corrected register mnemonic (was CANCTRL, is ERRSTAT).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 26                  | Content updates and enhancements throughout chapter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Revision History**

Table 3. MCF5213RM Rev 2 Errata (continued)

| Location   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix A | <ul> <li>Deleted entries for CACR, ACR0, and ACR1 registers.</li> <li>Corrected PPMRH and PPMRL addresses (IPSBAR+0x000C and IPSBAR+0x0018, respectively).</li> <li>Added leading zeros to addresses as necessary to adhere to four-digit address convention.</li> <li>Added RAMBAR register.</li> <li>Corrected misspelling of IPSBAR in address for the ICR034 and GPTACFORC registers.</li> <li>Changed mnemonic of register ICR45 to ICR045.</li> <li>Added ICR016 and ICR063 registers.</li> <li>Added global software and level n interrupt acknowledge registers.</li> <li>Corrected several typos in port pin data / set data register mnemonics.</li> <li>Corrected addresses of the LPDR, EPDR, EPFR, and GPTAPACNT registers.</li> <li>Corrected addresses of the DMA controller module registers to match the values in the text.</li> <li>Corrected general purpose timer register mnemonics (begin with GPT instead of GPTA).</li> <li>Corrected size of the pulse accumulator counter register (16 bits instead of 8).</li> <li>Deleted spaces in the mnemonics for the programmable interrupt controller registers.</li> <li>Added pulse width modulation channel duty and shutdown registers.</li> </ul> |

# 4 Revision History

Table 4 provides a revision history for this document.

**Table 4. Revision History Table**

| Rev. Number | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date of Release |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2           | Initial release, incorporating corrections listed in Table 3.                                                                                                                                                                                                                                                                                                                                                                                                     | 10/2006         |

| 3           | Various technical and other corrections as described in Table 2.                                                                                                                                                                                                                                                                                                                                                                                                  | 03/2007         |

| 4           | Various technical and other corrections as described in Table 2.      Added missing corrections against the following entities to Table 2:     Table 3-1     Figure 3-5     Table 3-2     Figure 3-7     Figure 3-8     Section 3.4     Table 5-1     Section 5.2.1     Table 26-4     Table 26-10     Figure 26-8     Table 26-22     Section 26.6.2      Added missing corrections against the following entities to Table 3:     Section 3.4     Section 3.6.2 | 04/2010         |

| 5           | Corrected errors in Chapter "Clock Module" and "FlexCAN"                                                                                                                                                                                                                                                                                                                                                                                                          | 11/2011         |

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011. All rights reserved.

Document Number: MCF5213RMAD

Rev. 5 11/2011