# Thermal Management Unit Usage

Rev. 0 — 27 April 2022 Application Note

### 1 Overview

This application note introduces the LS1xxxx and LS2xxxx devices Thermal Management Unit (TMU). It covers the topics, such as explanation of NXP TMU functional blocks and how to operate, program, and configure them. Later the SDK 2.0 solution is described followed by test examples and usage cases.

## 2 TMU operation model

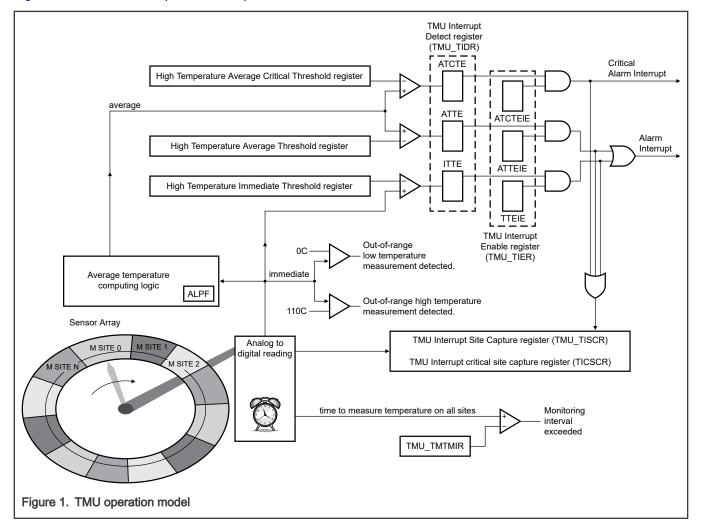

### Figure 1 shows the overall operation concept of the TMU.

#### Contents

| 1    | Overview                        | . 1 |

|------|---------------------------------|-----|

| 2    | TMU operation model             | .1  |

| 3    | Initialization procedure        | . 4 |

| 1    | Using U-Boot and Linux commands | s   |

|      | to read temperature             | 11  |

| 5    | Related documentation           | 13  |

| 3    | Revision history                | 13  |

| egal | information                     | 14  |

### 2.1 Sensor array

Each LSxxxx chip has several temperature sensors strategically positioned under major logic block. For example, LS1043 has 5 sensors as shown in Table 1.

Table 1. Sensor placement

| Temperature sensor ID | Placement                                           |  |

|-----------------------|-----------------------------------------------------|--|

| 0                     | Near DDR controller                                 |  |

| 1                     | Near SerDes                                         |  |

| 2                     | Near Frame manager                                  |  |

| 3                     | Near Arm <sup>®</sup> Cortex <sup>®</sup> -A53 core |  |

| 4                     | SEC                                                 |  |

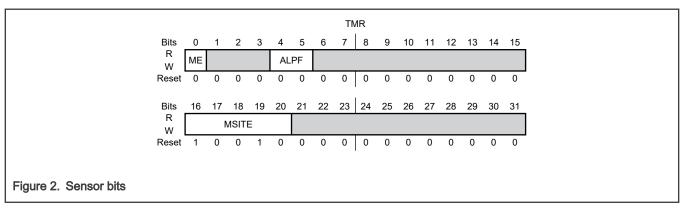

User can enable each site by setting a bit in the TMR[MSITE] bits. For example, to enable sensors near A53 and DDR controller, MSITE[0-4] should be 5'b10010. Thus, with monitoring mode disabled, ME = 0 and ALPF = 2'b00, the TMR bit settings are shown in the figure below.

The sensors are selected periodically and the temperature computation takes some time for each temperature sensor. If the periodic measurement interval divided by the number of enabled sensors is more than the time required to compute temperature, then TMU goes to the low-power mode until next sensor interval-starting time. On the other hand, if it is less than the computation time then the "monitoring interval exceeded" error bit is set in the TSR[MIE].

### 2.2 Analog to digital reading

The captured reading by the Analog to digital converter is passed to the following:

- · Average temperature computing logic

- · Instantaneous out of range high/low comparators

- High temperature-immediate threshold comparison logic

- · Instantaneous reading registers

- · Monitoring and reporting logic

If the instantaneous reading goes beyond or below 110 °C or 0 °C, then the TSR[ORL, ORH] bits are set but no interrupt is generated.

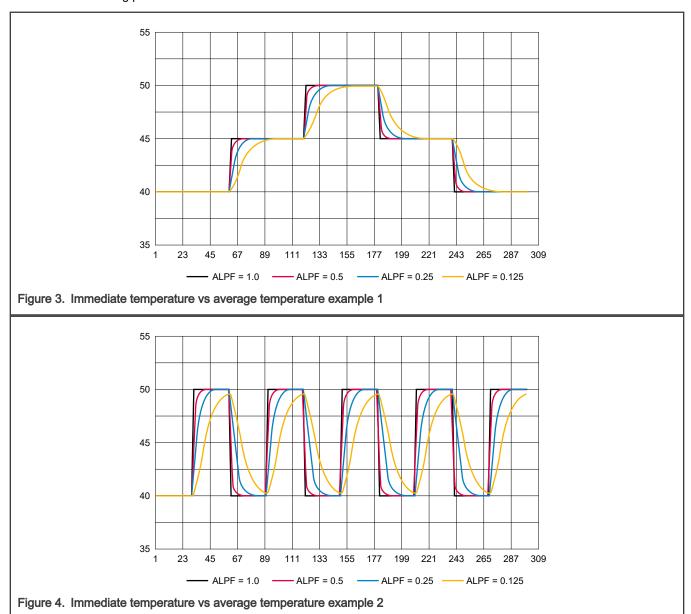

The average temperature computing logic presents an average reading as a function of the previous readings multiplied by a factor set by TMR[ALPF] parameter such that: Average temperature =  $ALPF \times Current\_Temp + (1 - ALPF) \times Average\_Temp$ .

If no previous average temperature is valid, current temperature is used. For proper operation, the ALPF optional values are 1.0, 0.5, 0.25, and 0.125. If ALPF is one, then the average temperature is the current instantaneous reading.

Application Note 2/16

Figure 3 and Figure 4 shows that the theoretical filtering action the ALPF values impacts on a two different "hypothetical" instantaneous reading profiles.

The average temperature then is compared against two stored threshold values in the following:

- · High temperature average critical threshold register

- · High temperature average threshold register

While the instantaneous current temperature reading is also compared against the value stored in the following:

· High temperature-immediate threshold register

If the average or instantaneous temperature value exceeds the limit values stored in the threshold registers, the TMU interrupt detect register TIDR[ITTE, ATTE, ATCTE] bits are set.

Besides, detecting the set, if the corresponding TMU interrupt enable register bits TIER[ITTEIE, ATTEIE, ATCTEIE] are enabled. A critical interrupt is generated if bit TIER [ATCTE] is set, or an alarm interrupt is generated if TIER [ITTE], or TIER [ATCTE] is set given that their corresponding TIDR bits were set too.

The interrupt handler tells which sensor site temperature reading has exceeded the threshold value by reading the TMU interrupt site capture register TISCR or the TMU interrupt critical site capture register.

## 3 Initialization procedure

In general, customers are given initialization data in the chip reference manual and SW driver use them as is. The TMU had internal array that holds calibration data and is structured in four ranges as listed in Table 2.

Table 2. Initialization data array

| TTRnCR region                        | Array address to TTCFGR | Array data to TSCFGR |  |

|--------------------------------------|-------------------------|----------------------|--|

| TTR0CR, 12 points at 0 °C. Each row  | 0x0000000               | 0x00000023           |  |

| represents an increment by 4         | 0x0000001               | 0x0000002A           |  |

|                                      | 0x00000002              | 0x00000031           |  |

|                                      | 0x0000003               | 0x00000037           |  |

|                                      | 0x0000004               | 0x0000003E           |  |

|                                      | 0x0000005               | 0x00000044           |  |

|                                      | 0x0000006               | 0x0000004B           |  |

|                                      | 0x0000007               | 0x00000051           |  |

|                                      | 0x00000008              | 0x00000058           |  |

|                                      | 0x0000009               | 0x0000005E           |  |

|                                      | 0x000000A               | 0x0000065            |  |

|                                      | 0х000000В               | 0x0000006B           |  |

| TTR1CR, 10 points at 42 °C. Each row | 0x00010000              | 0x00000023           |  |

| represents an increment by 4         | 0x00010001              | 0x0000002B           |  |

|                                      | 0x00010002              | 0x00000033           |  |

|                                      | 0x00010003              | 0x0000003B           |  |

|                                      | 0x00010004              | 0x0000043            |  |

|                                      | 0x00010005              | 0x0000004B           |  |

|                                      | 0x00010006              | 0x00000054           |  |

|                                      | 0x00010007              | 0x0000005C           |  |

|                                      | 0x00010008              | 0x0000064            |  |

|                                      | 0x00010009              | 0x000006C            |  |

| TTR2CR, 7 points at 76 °C. Each row  | 0x00020000              | 0x00000021           |  |

| represents an increment by 4         | 0x00020001              | 0x0000002C           |  |

|                                      | 0x00020002              | 0x00000036           |  |

|                                      | 0x00020003              | 0x0000040            |  |

|                                      | 0x00020004              | 0x0000004B           |  |

Table 2. Initialization data array (continued)

| TTRnCR region                       | Array address to TTCFGR | Array data to TSCFGR |

|-------------------------------------|-------------------------|----------------------|

|                                     | 0x00020005              | 0x00000055           |

|                                     | 0x00020006              | 0x0000005F           |

| TTR3CR, 8 points at 98 °C. Each row | 0x00030000              | 0x0000013            |

| represents an increment by 4        | 0x00030001              | 0x000001D            |

|                                     | 0x00030002              | 0x00000028           |

|                                     | 0x00030003              | 0x00000032           |

|                                     | 0x00030004              | 0x000003D            |

|                                     | 0x00030005              | 0x0000047            |

|                                     | 0x00030006              | 0x00000052           |

|                                     | 0x00030007              | 0x0000005C           |

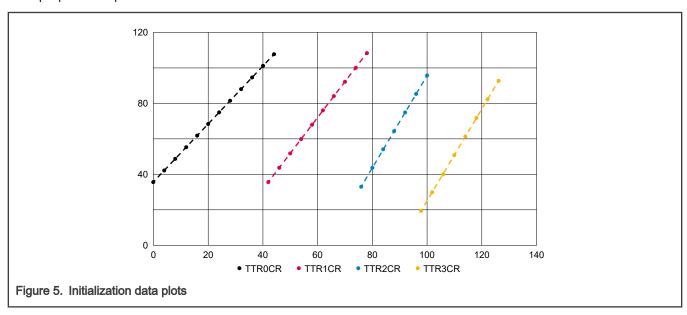

A simple plot of the previous tabulated data is shown below.

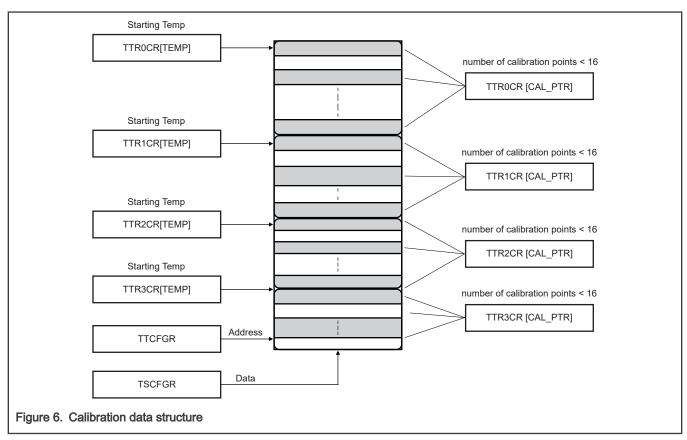

The figure below illustrates the calibration data structure.

In the above figure, the bulk of array is a 64-entry arranged in 4 sixteen blocks, where each TTRnCR register carries information about this 16 entries block, namely the starting temperature of the first entry and the total number of entries -1, that are programed out of 16 entries. Users typically know the total number based on the information provided by the chip reference manual. For example, in the LS1043A Reference Manual we see the below starting temperatures and number of points which results in the corresponding TTRnCR shown in Table 3.

Table 3. Temperature calibration points

| 12 points => 0xB | Starts from 0C => 0x0 | TTR0CR=0x000B0000 |

|------------------|-----------------------|-------------------|

| 10 points => 0x9 | Starts at 42C => 0x2A | TTR1CR=0x0009002A |

| 7 points => 0x6  | Starts at 76C => 0x4c | TTR2CR=0x0006004C |

| 8 points => 0x7  | Starts at 98C => 0x62 | TTR3CR=0x00070062 |

The process for programming the calibration table is described below.

- 1. Disable the monitoring mode, TMR[ME]=0 (default).

- 2. Program TTR0CR=0x000B0000, TTR1CR=0x0009002A, TTR2CR=0x0006004C, and TTR3CR=0x00070062.

- 3. Write the temperature configuration register (TTCFGR).

- 4. Write the sensor configuration register (TSCFGR).

- 5. Repeat steps 3 to 4 for all temperatures as defined in Table 3.

7 / 16

Table 4. Example U-Boot commands that initialize TMU

| Example of a U-Boot series of command that initializes TMU | Comments                                                                                   |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| #====Load init table ===                                   | Notice that there is endianness byte swap of the word contents when we type U-Boot command |

| #==========                                                | 3,                                                                                         |

| mw 0x1f00000 0x0                                           |                                                                                            |

| mw 0x1f00f10 0x00000b00                                    |                                                                                            |

| mw 0x1f00f14 0x2a000900                                    |                                                                                            |

| mw 0x1f00f18 0x4c000600                                    |                                                                                            |

| mw 0x1f00f1c 0x62000700                                    |                                                                                            |

| #                                                          |                                                                                            |

| #== TTR0CR, 12 points at 0°C ===                           |                                                                                            |

| #{0x0000000, 0x00000023}                                   |                                                                                            |

| mw 0x1f00080 0x00000000                                    |                                                                                            |

| mw 0x1f00084 0x23000000                                    |                                                                                            |

| #I0v00000001 0v0000002A)                                   |                                                                                            |

| #{0x00000001, 0x0000002A}<br>mw 0x1f00080 0x01000000       |                                                                                            |

| mw 0x1f00080 0x0 f0000000<br>mw 0x1f00084 0x2a000000       |                                                                                            |

| TIM GATIOGGG I GAZGGGGGG                                   |                                                                                            |

| #{0x00000002, 0x00000031}                                  |                                                                                            |

| mw 0x1f00080 0x02000000                                    |                                                                                            |

| mw 0x1f00084 0x31000000                                    |                                                                                            |

| Wa aaaaaaa a aaaaaa                                        |                                                                                            |

| #{0x00000003, 0x00000037}                                  |                                                                                            |

| mw 0x1f00080 0x03000000<br>mw 0x1f00084 0x37000000         |                                                                                            |

| 11W 0x1100004 0x37000000                                   |                                                                                            |

| #{0x00000004, 0x0000003E}                                  |                                                                                            |

| mw 0x1f00080 0x04000000                                    |                                                                                            |

| mw 0x1f00084 0x3e000000                                    |                                                                                            |

| #10, 0000000F 0, 00000044)                                 |                                                                                            |

| #{0x00000005, 0x00000044}<br>mw 0x1f00080 0x05000000       |                                                                                            |

| mw 0x1f00080 0x05000000<br>mw 0x1f00084 0x44000000         |                                                                                            |

| THE CATHOUGH CATTOUCCO                                     |                                                                                            |

| #{0x0000006, 0x0000004B}                                   |                                                                                            |

| mw 0x1f00080 0x06000000                                    |                                                                                            |

| mw 0x1f00084 0x4b000000                                    |                                                                                            |

| #{0x0000007, 0x00000051}                                   |                                                                                            |

| #{0x00000007, 0x000000051}<br>mw 0x1f00080 0x07000000      |                                                                                            |

| mw 0x1f00084 0x51000000                                    |                                                                                            |

| 5x 10000 1 0x0 100000                                      |                                                                                            |

Table 4. Example U-Boot commands that initialize TMU

| Example of a U-Boot series of command that initializes TMU | Comments |

|------------------------------------------------------------|----------|

| #fo_00000000_0_00000050\                                   |          |

| #{0x00000008, 0x00000058}                                  |          |

| mw 0x1f00080 0x08000000                                    |          |

| mw 0x1f00084 0x58000000                                    |          |

| #{0x0000009, 0x0000005E}                                   |          |

| mw 0x1f00080 0x09000000                                    |          |

| mw 0x1f00084 0x5e000000                                    |          |

| TIM EXTINGED TOXOGGGGGGG                                   |          |

| #{0x0000000A, 0x00000065}                                  |          |

| mw 0x1f00080 0x0a000000                                    |          |

| mw 0x1f00084 0x65000000                                    |          |

|                                                            |          |

| #{0x0000000B, 0x0000006B}                                  |          |

| mw 0x1f00080 0x0b000000                                    |          |

| mw 0x1f00084 0x6b000000                                    |          |

|                                                            |          |

| #======== <br>                                             |          |

| #===TTR1CR, 10 points at 42°C====                          |          |

|                                                            |          |

| #{0x00010000, 0x00000023}                                  |          |

| mw 0x1f00080 0x00000100                                    |          |

| mw 0x1f00084 0x23000000                                    |          |

|                                                            |          |

| #{0x00010001, 0x0000002B}                                  |          |

| mw 0x1f00080 0x01000100                                    |          |

| mw 0x1f00084 0x2b000000                                    |          |

| #{0x00010002, 0x00000033}                                  |          |

| mw 0x1f00080 0x02000100                                    |          |

| mw 0x1f00084 0x33000000                                    |          |

|                                                            |          |

| <br> #{0x00010003, 0x0000003B}                             |          |

| mw 0x1f00080 0x03000100                                    |          |

| mw 0x1f00084 0x3b000000                                    |          |

|                                                            |          |

| #{0x00010004, 0x00000043}                                  |          |

| mw 0x1f00080 0x04000100                                    |          |

| mw 0x1f00084 0x43000000                                    |          |

|                                                            |          |

Table 4. Example U-Boot commands that initialize TMU

| Example of a U-Boot series of command that initializes TMU | Comments |

|------------------------------------------------------------|----------|

| #{0x00010005, 0x0000004B}                                  |          |

| mw 0x1f00080 0x05000100                                    |          |

| mw 0x1f00084 0x4b000000                                    |          |

|                                                            |          |

| #{0x00010006, 0x00000054}                                  |          |

| mw 0x1f00080 0x06000100                                    |          |

| mw 0x1f00084 0x54000000                                    |          |

|                                                            |          |

| #{0x00010007, 0x0000005C}                                  |          |

| mw 0x1f00080 0x07000100                                    |          |

| mw 0x1f00084 0x5c000000                                    |          |

| #{0x00010008, 0x00000064}                                  |          |

| mw 0x1f00080 0x08000100                                    |          |

| mw 0x1f00084 0x64000000                                    |          |

| THIN GATIOGOGY GACTOGOGG                                   |          |

| <br> #{0x00010009, 0x0000006C}                             |          |

| mw 0x1f00080 0x09000100                                    |          |

| mw 0x1f00084 0x6c000000                                    |          |

|                                                            |          |

| #============                                              |          |

| #====TTR2CR, 7 points at 76°C =====                        |          |

| <br> #{0x00020000, 0x00000021}                             |          |

| mw 0x1f00080 0x00000200                                    |          |

| mw 0x1f00084 0x21000000                                    |          |

|                                                            |          |

| #{0x00020001, 0x0000002C}                                  |          |

| mw 0x1f00080 0x01000200                                    |          |

| mw 0x1f00084 0x2c000000                                    |          |

|                                                            |          |

| #{0x00020002, 0x00000036}                                  |          |

| mw 0x1f00080 0x02000200                                    |          |

| mw 0x1f00084 0x36000000                                    |          |

|                                                            |          |

| #{0x00020003, 0x00000040}                                  |          |

| mw 0x1f00080 0x03000200                                    |          |

| mw 0x1f00084 0x40000000                                    |          |

|                                                            |          |

Table 4. Example U-Boot commands that initialize TMU

| Example of a U-Boot series of command that initializes TMU | Comments |

|------------------------------------------------------------|----------|

| #{0x00020004, 0x0000004B}                                  |          |

| mw 0x1f00080 0x04000200                                    |          |

| mw 0x1f00084 0x4b000000                                    |          |

|                                                            |          |

| #{0x00020005, 0x00000055}                                  |          |

| mw 0x1f00080 0x05000200<br>mw 0x1f00084 0x55000000         |          |

| 111W 0X1100064 0X33000000                                  |          |

| <br> #{0x00020006, 0x0000005F}                             |          |

| mw 0x1f00080 0x06000200                                    |          |

| mw 0x1f00084 0x5f000000                                    |          |

|                                                            |          |

| #===TTR3CR, 8 points at 98°C=====                          |          |

|                                                            |          |

| #{0x00030000, 0x00000013}                                  |          |

| mw 0x1f00080 0x00000300                                    |          |

| mw 0x1f00084 0x13000000                                    |          |

| #{0x00030001, 0x0000001D}                                  |          |

| mw 0x1f00080 0x01000300                                    |          |

| mw 0x1f00084 0x1d000000                                    |          |

|                                                            |          |

| #{0x00030002, 0x00000028}                                  |          |

| mw 0x1f00080 0x02000300                                    |          |

| mw 0x1f00084 0x28000000                                    |          |

| #(0,,000,2000,2,0,,000,000,2,2)                            |          |

| #{0x00030003, 0x00000032}<br>mw 0x1f00080 0x03000300       |          |

| mw 0x1f00084 0x32000000                                    |          |

|                                                            |          |

| #{0x00030004, 0x0000003D}                                  |          |

| mw 0x1f00080 0x04000300                                    |          |

| mw 0x1f00084 0x3d000000                                    |          |

| #{0\00030005_0\00000047}                                   |          |

| #{0x00030005, 0x00000047}<br>mw 0x1f00080 0x05000300       |          |

| mw 0x1f00084 0x47000000                                    |          |

|                                                            |          |

| #{0x00030006, 0x00000052}                                  |          |

| mw 0x1f00080 0x06000300                                    |          |

| mw 0x1f00084 0x52000000                                    |          |

Table 4. Example U-Boot commands that initialize TMU

| Example of a U-Boot series of command that initializes TMU | Comments |

|------------------------------------------------------------|----------|

|                                                            |          |

| #{0x00030007, 0x0000005C}                                  |          |

| mw 0x1f00080 0x07000300<br>mw 0x1f00084 0x5c000000         |          |

|                                                            |          |

|                                                            |          |

| #============<br>                                          |          |

|                                                            |          |

| #===1 seconds timer monitor=====                           |          |

|                                                            |          |

| mw 0x1f00008 0x08000000                                    |          |

|                                                            |          |

| <br> #======                                               |          |

|                                                            |          |

| #=====Enable TMU and all sites=====                        |          |

| Enable Title did director                                  |          |

| 0.4f00000 0.00f00000                                       |          |

| mw 0x1f00000 0x00f80080                                    |          |

|                                                            |          |

| #=========<br>                                             |          |

|                                                            |          |

| md 0x1f00100                                               |          |

|                                                            |          |

## 4 Using U-Boot and Linux commands to read temperature

Use the following commands to do LS1043ARDB temperature measurement.

Table 5. Commands to read temperature

| In U-Boot mode | >sensors                                                         |

|----------------|------------------------------------------------------------------|

| In Linux       | root@ls1043ardb:~# cat /sys/class/thermal/thermal_zone0/<br>temp |

#### NOTE

The sensors command in U-Boot does not read the TMU. Instead, it reads the I2C chip that reads the thermal diode temperature which should be close to the TMU reading when in Linux mode. The provided initialization sequence in the previous section allows user to read TMU temperature while being in U-Boot without the need to boot Linux. Thus, you can display the TMU registers with this command example:

and then read all TMU sensors readings, the average and the current per memory map below:

Table 6. LS1043A TMU memory map example at TMU base address 0x01F0\_0000

| Offset | Register                                                   | Width | Access | Example Reading                                     |

|--------|------------------------------------------------------------|-------|--------|-----------------------------------------------------|

| 100h   | TMU report immediate temperature site register 0 (TRITSR0) | 32    | RO     | 0x25000080  Valid reading  temp = 25Hex = 37 °C     |

| 104h   | TMU report average temperature site register 0 (TRATSR0)   | 32    | RO     | 0x25000080  Valid reading  temp = 25Hex = 37 °C     |

| 110h   | TMU report immediate temperature site register 1 (TRITSR1) | 32    | RO     | 0x23000080<br>Valid reading<br>temp = 23Hex = 35 °C |

| 114h   | TMU report average temperature site register 1 (TRATSR1)   | 32    | RO     | 0x23000080<br>Valid reading<br>temp = 23Hex = 35 °C |

| 120h   | TMU report immediate temperature site register 2 (TRITSR2) | 32    | RO     | 0x24000080  Valid reading  temp = 24Hex = 36 °C     |

| 124h   | TMU report average temperature site register 2 (TRATSR2)   | 32    | RO     | 0x24000080<br>Valid reading<br>temp = 24Hex = 36 °C |

| 130h   | TMU report immediate temperature site register 3 (TRITSR3) | 32    | RO     | 0x24000080  Valid reading  temp = 24Hex = 36 °C     |

| 134h   | TMU report average temperature site register 3 (TRATSR3)   | 32    | RO     | 0x24000080<br>Valid reading                         |

Table 6. LS1043A TMU memory map example at TMU base address 0x01F0\_0000 (continued)

| Offset | Register                                                   | Width | Access | Example Reading                                     |

|--------|------------------------------------------------------------|-------|--------|-----------------------------------------------------|

|        |                                                            |       |        | temp = 24Hex = 36 °C                                |

| 140h   | TMU report immediate temperature site register 4 (TRITSR4) | 32    | RO     | 0x23000080  Valid reading  temp = 23Hex = 35 °C     |

| 144h   | TMU report average temperature site register 4 (TRATSR4)   | 32    | RO     | 0x23000080<br>Valid reading<br>temp = 23Hex = 35 °C |

### 5 Related documentation

Refer to the following documents. Contact your NXP sales representative for access to any documents that are not publicly available on the NXP external website.

- AN4787 Temperature Measurements Using an On-Die Thermal Diode

- LS1xxx and LS2xxx reference manuals and data sheets

## 6 Revision history

This table summarizes the revisions to this document.

Table 7. Revision history

| Revision | Date          | Description     |

|----------|---------------|-----------------|

| 0        | 27 April 2022 | Initial release |

### Legal information

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

Application Note 14 / 16

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile — are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

Airfast — is a trademark of NXP B.V.

**Bluetooth** — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

**Cadence** — the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All rights reserved worldwide.

CodeWarrior — is a trademark of NXP B.V.

ColdFire — is a trademark of NXP B.V.

ColdFire+ - is a trademark of NXP B.V.

EdgeLock — is a trademark of NXP B.V.

EdgeScale — is a trademark of NXP B.V.

EdgeVerse — is a trademark of NXP B.V.

eIQ — is a trademark of NXP B.V.

FeliCa — is a trademark of Sony Corporation.

Freescale — is a trademark of NXP B.V.

HITAG — is a trademark of NXP B.V.

ICODE and I-CODE — are trademarks of NXP B.V.

Immersiv3D — is a trademark of NXP B.V.

12C-bus — logo is a trademark of NXP B.V.

Kinetis — is a trademark of NXP B.V.

Layerscape — is a trademark of NXP B.V.

Mantis — is a trademark of NXP B.V.

MIFARE — is a trademark of NXP B.V.

MOBILEGT — is a trademark of NXP B.V.

NTAG — is a trademark of NXP B.V.

Processor Expert — is a trademark of NXP B.V.

QorlQ — is a trademark of NXP B.V.

SafeAssure — is a trademark of NXP B.V.

SafeAssure — logo is a trademark of NXP B.V.

StarCore — is a trademark of NXP B.V.

Synopsys — Portions Copyright © 2021 Synopsys, Inc. Used with permission. All rights reserved.

Tower — is a trademark of NXP B.V.

UCODE — is a trademark of NXP B.V.

VortiQa — is a trademark of NXP B.V.

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 27 April 2022 Document identifier: AN12310