Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

Rev. 3 — 10 March 2023

Application note

#### **Document information**

| Information | Content                                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | FXLS8964AF, FXLS8967AF, FXLS8968AF, FXLS8974CF, FXLS8971CF, FXLS8961AF, 3-axis accelerometer, Sensor Data Change Detection (SDCD), inertial event detection |

| Abstract    | This document describes details about the Sensor Data Change<br>Detection (SDCD) block within the FXLS896xAF and FXLS897xCF 3-axis<br>accelerometer devices |

### **Revision history**

| Rev | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v.3 | 20230310 | <ul> <li>Document title: revised the title</li> <li>Keywords and Abstract: revised keywords and abstract on the first page.</li> <li><u>Section 1</u>, revised the first sentence.</li> <li><u>Section 3</u>, revised the first paragraph into three paragraphs.</li> <li><u>Section 3.1</u>, revised the "Observation" paragraph.</li> <li><u>Section 3.4</u>, revised the "Observation" paragraph.</li> <li><u>Section 3.5</u>, revised the "Observation" paragraph.</li> <li><u>Section 3.5</u>, revised the "Deservation" paragraph.</li> </ul> |

| v.2 | 20201030 | <ul> <li>Revised the document title from "FXLS89x2 Sensor Data Change Detection<br/>(SDCD) block overview and examples" to "FXLS896xAF / FXLS897xCF Sensor<br/>Data Change Detection (SDCD) block overview and example."</li> <li>Global: revised "FXLS89x2" to "FXLS896xAF and FXLS897xCF" or "FXLS896xAF/<br/>FXLS897xCF" throughout the document.</li> </ul>                                                                                                                                                                                     |

| v.1 | 20180201 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### 1 Introduction

The Sensor Data Change Detection (SDCD) block of FXLS896xAF and FXLS897xCF accelerometer family is an efficient and flexible inertial event detection function with the ability to detect inertial events such as motion/no-motion, high-g/low-g, tap, freefall and transient acceleration events, etc. This application note discusses in detail the features of the embedded block in real world application use cases. A series of examples with sample register configurations is covered to help users get started quickly.

### 2 SDCD block

#### 2.1 Function overview

The SDCD function within FXLS896xAF and FXLS897xCF incorporates a flexible digital window comparator useful for implementing several different interrupt event generation functions. The SDCD block operates in either relative or absolute modes and features user programmable thresholds, debounce time, event polarity detection and interrupt generation logic.

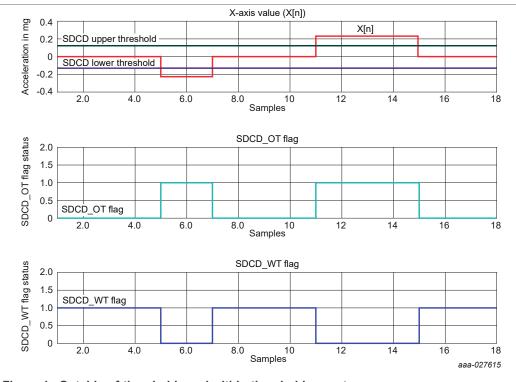

Simply stated, the acceleration data input (X[n], for example) to the SDCD block is compared against a set of user programmable upper and lower thresholds (see Figure 1) in absolute or relative mode. For simplicity, only the absolute mode of operation is presented. The relative mode of operation is covered in <u>Section 2.5 "Reference update modes"</u>.

- When an outside-of-thresholds (OT) event is enabled in the SDCD configuration register, a motion detection interrupt is generated whenever the input signal is greater in magnitude than the upper or lower threshold for the set debounce time (see <u>Section 2.3 "Programmable debounce counter"</u> for more details). In this example, the debounce counter is set to zero and the interrupt is generated as soon as the condition evaluates to true.

- When a within-thresholds (WT) event is enabled in the SDCD configuration register, a

motion detection interrupt is generated whenever the input signal is between the upper

and lower thresholds.

Application note

Figure 1. Outside-of-thresholds and within-thresholds event

**Note:** The SDCD OT and WT interrupts can be triggered in real time or in latched mode. Details on interrupt logic are described in <u>Section 2.4 "Interrupt logic"</u>.

#### **Block Diagram**

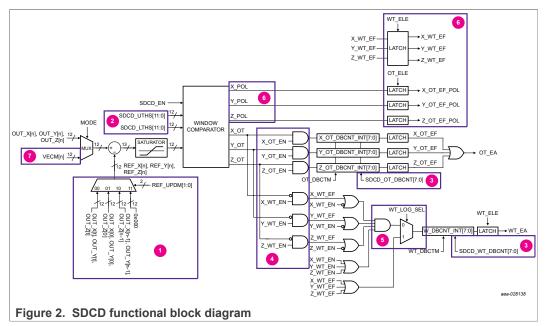

The high level SDCD block diagram is shown in Figure 2.

- 1. Relative or Absolute SDCD modes. Refer to Section 2.5 "Reference update modes".

- 2. Programmable upper or lower thresholds. The sensitivity of the threshold registers is same as the device's sensitivity for the currently selected full scale range (FSR).

- Independent programmable debounce counters for both OT and WT event conditions. The counter time step is equal to the currently selected output data rate (ODR) period for the device.

- 4. Independent selection of axes for OT and WT interrupt logic.

- 5. WT event logic selection (AND/OR) for the enabled axes.

- 6. Event polarity detection and interrupt latching feature.

- 7. Vector magnitude result can be optionally used as an input to the SDCD function using the X-Axis channel.

#### 2.2 **Programmable thresholds**

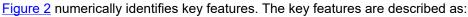

The SDCD block's upper and lower thresholds are encoded in 12-bit 2's complement format from addresses 33h to 36h (see <u>Table 1</u>). The scaling for the threshold registers is the same as the sensitivity of the selected FSR. The FSR is configured in the SENS\_CONFIG1 (15h) register.

**Example:** If FSR is set to  $\pm 16$  g mode, 1 LSB in the SDCD threshold register corresponds to 7.81 mg.

#### Threshold in mg = Threshold in counts × sensitivity

**Note:** The SDCD\_UTHS[11:0] must always be set to a higher value than SDCD\_LTHS[11:0] to ensure the SDCD circuit functions correctly and produces meaningful results.

| Name          | Address | Access | Comment                                                  | Accessibility                               |

|---------------|---------|--------|----------------------------------------------------------|---------------------------------------------|

| SDCD_LTHS_LSB | 33h     | R/W    | SDCD lower threshold<br>value LSB - sdcd_lths[7:0<br>]   | Read: always<br>Write: Standby mode<br>only |

| SDCD_LTHS_MSB | 34h     | R/W    | SDCD lower threshold<br>value MSB - sdcd_<br>lths[11:8]. | Read: always<br>Write: Standby mode<br>only |

| SDCD_UTHS_LSB | 35h     | R/W    | SDCD upper threshold<br>value LSB - sdcd_<br>uths[7:0]   | Read: always<br>Write: Standby mode<br>only |

| SDCD_UTHS_MSB | 36h     | R/W    | SDCD upper threshold<br>value MSB - sdcd_<br>uths[11:8]  | Read: always<br>Write: Standby mode<br>only |

Table 1. SDCD programmable threshold registers

#### 2.3 Programmable debounce counter

Two sets of programmable debounce counter registers, SDCD\_OT\_DBCNT and SDCD\_WT\_DBCNT, are available for OT and WT event detection. The counter step period is equal to the selected ODR period in low power mode (LPM) and high performance mode (HPM) modes, and to the effective ODR period (measurement + idle time) in flexible performance mode (FPM) mode.

**Note:** When BT\_MODE = VDD, the use of HPM and FPM modes is not advised. Use only the default LPM mode.

Debounce period (ms) = Debounce count × (1/ODR(Hz))

These registers set the minimum number of debounce counter periods needed to recognize an SDCD event condition as true.

For example, when ODR = 100 Hz (10 ms period), and debounce count for the OT event is 5, then the debounce time period is  $5 \times 10 = 50$  ms.

A transition from Standby to Active, Active to Standby, or Auto-WAKE/SLEEP mode automatically resets the internal SDCD OT and WT counters.

| Name          | Address | Access | Comment                                                                 | Accessibility                               |

|---------------|---------|--------|-------------------------------------------------------------------------|---------------------------------------------|

| SDCD_OT_DBCNT | 31h     | R/W    | Debounce count<br>threshold register<br>for SDCD OT event<br>detection. | Read: always<br>Write: Standby mode<br>only |

| SDCD_WT_DBCNT | 32h     | R/W    | Debounce count<br>threshold register<br>for SDCD WT event<br>detection. | Read: always<br>Write: Standby mode<br>only |

Table 2.

SDCD programmable timer registers

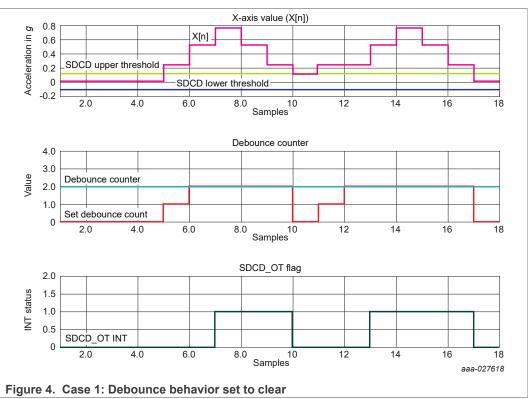

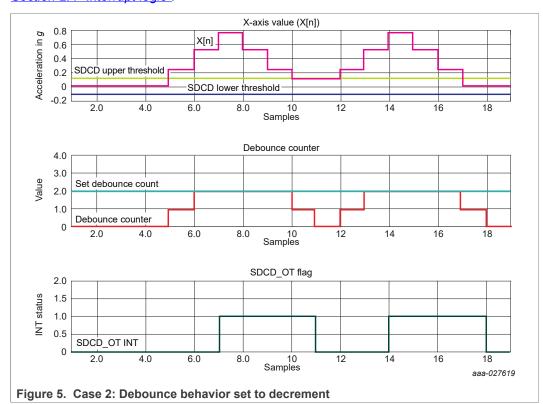

**Example:** Consider the graph shown in Figure 4, showing the OT event enabled, ODR is set to 100 Hz and debounce time is set to 20 ms (i.e. SDCD\_OT\_DBCNT equals 2). Thus, when the input signal is greater than the SDCD threshold for the set debounce time period, an interrupt is flagged.

When the debounce count is set to 0 (Figure 1), the interrupt is generated as soon as the input signal meets the threshold criteria for the OT or WT events. The interrupt is also cleared as soon as the condition becomes false.

#### Debounce count behavior:

#### Note: The debounce counter can be decremented without clearing the interrupt.

The debounce counters can be programmed to either decrement or clear once the event condition becomes false. See examples below. The debounce counter behavior is selected using the OT\_DBCTM and WT\_DBCTM bits in the SDCD\_CONFIG2 (address 30h) register.

#### Table 3. SDCD\_CONFIG2 register

| Bit                 | 7       | 6      | 5        | 4     | 3     | 2       | 1    | 0       |

|---------------------|---------|--------|----------|-------|-------|---------|------|---------|

| Read                | SDCD_EN | REF_UF | PDM[1:0] | OT_   | WT_   | WT_     | MODE | REF_UPD |

| Write               |         |        |          | DBCTM | DBCTM | LOG_SEL |      |         |

| Reset (BT_MODE = 0) | 0       | 0      | 0        | 0     | 0     | 0       | 0    | 0       |

| Reset (BT_MODE = 1) | 1       | 1      | 0        | 1     | 1     | 0       | 0    | 0       |

## In case 1, the debounce counter behavior is set to clear the event flag as soon as the condition becomes false.

With case 2, the debounce behavior is set to decrement. If the condition evaluates to false, the interrupt doesn't clear immediately but instead the debounce count decrements on every ODR period where the condition does not evaluate to true. Once the debounce counter reaches zero, the interrupt is cleared.

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

**Note:** In both cases, the interrupt event flag is not latched and reflects motion detection interrupts in real time. Further details on the interrupt generation logic are provided in Section 2.4 "Interrupt logic".

#### 2.4 Interrupt logic

Interrupt generation for OT and WT events can be enabled independently for each axis. This is done using the X/Y/Z\_OT\_EN and X/Y/Z\_WT\_EN bits in the SDCD\_CONFIG1 register (address 2Fh)

Table 4. SDCD\_CONFIG1 register

| Bit                  | 7      | 6      | 5       | 4       | 3       | 2       | 1       | 0       |

|----------------------|--------|--------|---------|---------|---------|---------|---------|---------|

| Read                 | OT ELE | WT ELE | X_OT_EN | Y_OT_EN | Z_OT_EN | X_WT_EN | Y_WT_EN | Z WT EN |

| Write                |        |        |         |         | 2_01_1  |         |         |         |

| Reset<br>BT_MODE = 0 | 0      | 0      | 0       | 0       | 0       | 0       | 0       | 0       |

| Reset<br>BT_MODE = 1 | 0      | 0      | 1       | 1       | 1       | 0       | 0       | 0       |

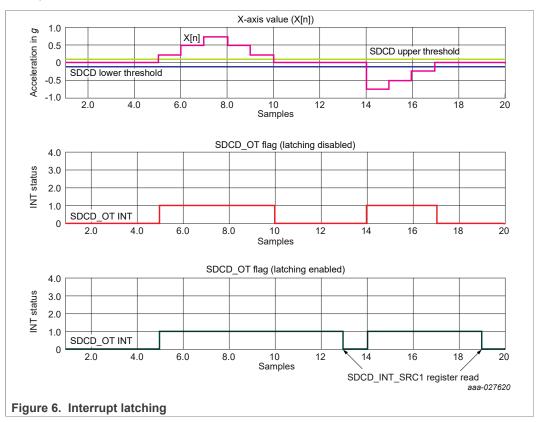

#### **Event latching:**

Setting the OT\_ELE, WT\_ELE bits in the SDCD\_CONFIG1 register latches the event interrupt. Once the interrupt is latched, the event flags (X/Y/Z\_OT\_EF, X/Y/Z\_WT\_EF) in the SDCD\_INT\_SRC1/2 registers can only be cleared by reading these interrupt source registers. Note that when latching is enabled, the event flag is only asserted when the event condition transitions from false to true, meaning once the event flag is

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

set, the event condition must first become false before a subsequent true event can be recognized again.

<u>Figure 6</u> illustrates the interrupt behavior when latching is enabled or disabled. In this example, the outside-of-thresholds event is enabled and debounce count is set to zero.

#### Interrupt usage when BT\_MODE pin state = VDD or GND

<u>Table 5</u> contains parameters worth noting while using interrupts from the SDCD block.

Table 5. Interrupt usage

| BT_MODE=VDD                                                                                                                                                              | BT_MODE=GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open drain                                                                                                                                                               | Push-pull                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Active low. Falling edge marks event detection                                                                                                                           | Active high. Rising edge marks event detection                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Motion detection interrupts can only be<br>routed to INT1 pin as only boot interrupt<br>can be routed to INT2.                                                           | Motion detection interrupts can be routed to either INT1 or INT2 pins                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Max ODR is 100 Hz because the data<br>ready interrupt is signalled for T <sub>PULSE-</sub><br><sub>MOT</sub> seconds (5 ms typ) for every data<br>sample.                | No limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| If interrupt is latched, the physical<br>interrupt will pulse for only 5 ms and will<br>retrigger again in the next ODR period (if<br>interrupt flag is still uncleared) | No such pulsing behavior for interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                          | <ul> <li>Open drain</li> <li>Active low. Falling edge marks event detection</li> <li>Motion detection interrupts can only be routed to INT1 pin as only boot interrupt can be routed to INT2.</li> <li>Max ODR is 100 Hz because the data ready interrupt is signalled for T<sub>PULSE-MOT</sub> seconds (5 ms typ) for every data sample.</li> <li>If interrupt is latched, the physical interrupt will pulse for only 5 ms and will retrigger again in the next ODR period (if</li> </ul> |

AN12004

9/21

#### Logic selection

The WT\_LOG\_SEL bit in the SDCD\_CONFIG2 register allows to do logical decisions (AND/OR) on the enabled axes. An example of use of this feature is detecting freefall (see <u>Section 3</u>), where a "within" threshold event has to be detected on all three axes at the same time for an interrupt to be triggered. The logical AND condition would be the appropriate WT logic setting for this use case.

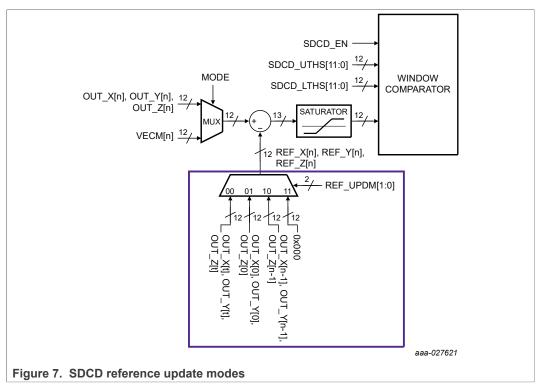

### 2.5 Reference update modes

The input to the window comparator is the difference between the current acceleration value and a programmable reference value as shown in <u>Figure 7</u>. Depending on the selected reference update mode, a corresponding reference value will be chosen. The mode selection is effected through the REF\_UPDM[1:0] bits in the SDCD\_CONFIG2 register.

#### REF\_UPDM[1:0] selection:

- 0b00: The function stores the first 12-bit X/Y/Z decimated and trimmed input data (OUT\_X/Y/Z[n=0]) as the internal REF\_X/Y/Z values after the function is enabled (SDCD\_EN is set to 1). The REF\_X/Y/Z values are updated with the current 12-bit X/Y/ Z decimated input data (OUT\_X/Y/Z[n]) at the time the SDCD\_OT\_EA flag transitions from false to true.

- 0b01: The function stores the first decimated and trimmed X/Y/Z acceleration input data (OUT\_X/Y/Z[n=0]) as the internal REF\_X/Y/Z values when the SDCD function is enabled; the REF\_X/Y/Z values are then held constant and never updated until the SDCD function is disabled and subsequently enabled, or asynchronously when the REF\_UPD bit is set by the host.

At any point, the internal reference values can be updated with the current X, Y, Z acceleration values by setting the trigger bit REF\_UPD in the SENS\_CONFIG2 register.

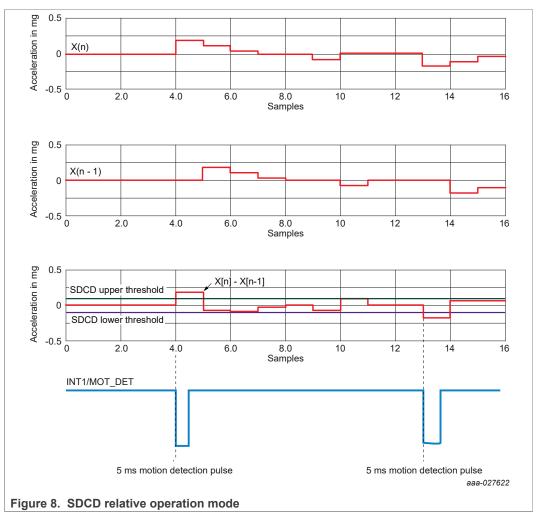

- 0b10: The function updates the SDCD\_REF\_X/Y/Z values with the current decimated and trimmed X/Y/Z acceleration input data after the function evaluation. This allows for acceleration slope detection with Data(n) to Data(n–1) to be used as the input to the window comparator. Figure 8 shows the SDCD block usage in relative mode.

- 0b11: The function uses a fixed value of 0 for each of the SDCD\_REF\_X/Y/Z registers, making the function operate in absolute comparison mode.(Example Figure 1, Figure 4, Figure 5 shows the SDCD block usage in absolute mode)

**Note:** It is possible to use the vector magnitude input to the SDCD block through the X-axis channel. The X-axis channel parameters  $(X/Y/Z_OT_EN, X/Y/Z_WT_EN)$  have to be used to act on the vector magnitude signal. The vector magnitude result is used as an input as soon as the MODE bit in SDCD\_CONFIG2 register is set, and the vector magnitude function is enabled by setting SENS\_CONFIG5[VECM\_EN] = 1.

#### 3 Example use cases

This section illustrates five popular dynamic motion based use cases ( $\underline{\text{Table 6}}$ ) and will cover sample register configuration steps (with BT\_MODE = GND) and device behavior for each case.

Refer to the specific use-cases in <u>Section 3.1</u> through <u>Section 3.5</u> for more details.

Note that the sample register configurations are limit tested and users can fine tune these configurations based on their requirements.

| Trigger      | Shake                                                           | Motion to<br>No-Motion              | Twist                             | Free-fall                | Jerk/<br>Transient/Tap        |

|--------------|-----------------------------------------------------------------|-------------------------------------|-----------------------------------|--------------------------|-------------------------------|

| Application  | Smart Inhaler                                                   | Smartwatch<br>deep sleep<br>mode    | Smartwatch<br>wake mode           | Human fall detection     | Smartwatch<br>menu cycling    |

| Action       | Indicate to the<br>user to shake<br>the unit well<br>before use | Deactivate<br>Smartwatch<br>display | Activate<br>Smartwatch<br>display | Send out a medical alert | Cycle through menu items      |

| OT/WT        | ОТ                                                              | WT                                  | WT                                | WT                       | ОТ                            |

| Axes Enabled | Х                                                               | XYZ                                 | XZ                                | XYZ                      | XYZ                           |

| WT_LOG_SEL   | OR                                                              | AND                                 | AND                               | AND                      | OR                            |

| Ref_updm     | 0b11<br>(absolute)                                              | 0b10<br>(Relative<br>N-(N-1))       | 0b01<br>(Relative-<br>fixed Ref)  | 0b11<br>(absolute)       | 0b10<br>(Relative<br>N-(N-1)) |

| UTHS         | 2.5 g                                                           | 0.1 g                               | -1 g                              | 0.2 g                    | 2 g                           |

| LTHS         | -2.5 g                                                          | -0.1 g                              | -3 g                              | -0.2 g                   | -2 g                          |

| Debounce     | 10 ms                                                           | 2.55 s                              | 10 ms                             | 100 ms                   | 0                             |

| ODR          | 400 Hz                                                          | 100 Hz                              | 200 Hz                            | 100 Hz                   | 25 Hz                         |

Table 6. SDCD configurations for example use cases

#### 3.1 Shake event detection

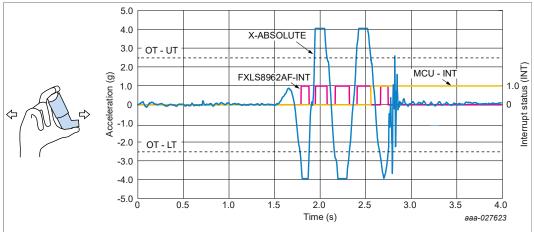

Example use case: Smart Inhaler - Indicate to the user to shake the unit well before use.

#### Motion and its signature:

A typical shake motion is unidirectional and involves four consecutive side to side shake movements of the device, each indicated by four half sine signatures on the shake axis (X Axis in this case). To detect the signature, a reasonably high data rate (400 Hz) is required and the SDCD block can be operated under absolute mode with threshold levels set to  $\pm 2.5$  g for identifying a shake event.

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

Figure 9. Shake motion and its signature

| Table 7 | Register | configuration | for shake | motion | event detection |

|---------|----------|---------------|-----------|--------|-----------------|

|         | register | configuration | IOI SHUKE | mouon  |                 |

| Register | Value | Description                                                                                                                               |

|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 15h      | 02h   | FSR = 4 g and Standby mode                                                                                                                |

| 17h      | 33h   | Wake ODR = 400 Hz and Sleep ODR = 400 Hz                                                                                                  |

| 2Fh      | 20h   | Enable X axis only for SDCD OT function                                                                                                   |

| 30h      | F0h   | Enable SDCD function, Enable Absolute Reference Mode and set OT<br>Debounce counter to clear immediately when threshold criteria is false |

| 31h      | 04h   | Debounce time = $4 \times (1/400) = 10$ ms                                                                                                |

| 33h      | FEh   | Registers 33h and 34h set the OT LOWER threshold. In this case it is set to                                                               |

| 34h      | FAh   | hex2dec (FAFE) × 1.95 mg/LSB = <b>-2.5 g</b> (1.95 mg/LSB in 4 g mode).                                                                   |

| 35h      | 02h   | Registers 35h and 36h set the OT UPPER threshold. In this case it is set to                                                               |

| 36h      | 05h   | hex2dec (0502) × 1.95mg/LSB = <b>+2.5</b> g                                                                                               |

| 20h      | A0h   | Enabling DRDY_EN and SDCD_OT_EN                                                                                                           |

| 21h      | 80h   | Routing DRDY interrupt to INT2 pin                                                                                                        |

| 15h      | 03h   | FSR = 4 g and ACTIVE = 1                                                                                                                  |

#### **Observation:**

The SDCD block triggers an interrupt every time the threshold of  $\pm 2.5$  g was met (with debounce time of 10 ms) and MCU can generate an interrupt after receiving four consecutive interrupts from the accelerometer which denotes the shake gesture.

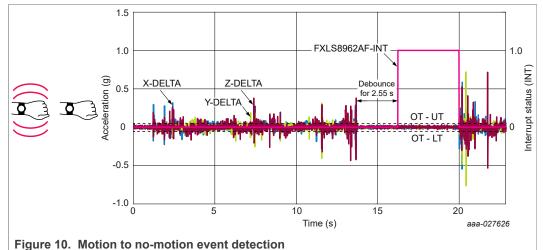

#### 3.2 Motion to no-motion event detection

**Example use case:** Put the MCU in smartwatch to deep sleep mode when the device is at rest.

#### Motion and its signature:

The transition from motion to no motion is a relatively simple activity to detect compared to other activities. WT detection in the SDCD block can be used on the axes in relative mode for a set debounce time to determine if no motion had occurred. In this example, to detect a motion to no-motion event, WT value of  $\pm 100$  mg is used and the debounce

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

count is set for at least 255 consecutive samples. When ODR=100 Hz, debounce time equals 2.55 s, meaning when there is no activity for 2.55 s, an interrupt is triggered.

•

| Table 8. Re | egister o | configuration for motion to no-motion event detection                                                             |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------|

| Register    | Value     | Description                                                                                                       |

| 15h         | 02h       | FSR = 4 g and Standby mode                                                                                        |

| 17h         | 55h       | Wake ODR = 100 Hz and Sleep ODR =100 Hz (Reg 16h = 00h low power mode by default)                                 |

| 2Fh         | 07h       | Enabling SDCD WT for all 3 axes X, Y, Z                                                                           |

| 30h         | C8h       | Enabling SDCD and Relative Data (N) – Data (N-1) mode for motion to no-<br>motion detection                       |

| 32h         | FFh       | Debounce time is 255 samples corresponding to 2.55 s for setting and clearing motion to no-motion event detection |

| 33h         | CCh       | Registers 33h and 34h set the OT LOWER threshold. In this case it is set to                                       |

| 34h         | FFh       | hex2dec (FFCC) × 1.95 mg/LSB = <b>–100 mg</b> (1.95 mg/LSB in 4 g mode).                                          |

| 35h         | 34h       | Registers 35h and 36h set the OT UPPER threshold. In this case it is set to                                       |

| 36h         | 00h       | hex2dec (0034) × 1.95 mg/LSB = <b>+100 mg</b>                                                                     |

| 20h         | 90h       | Enabling DRDY_EN and SDCD_WT_EN                                                                                   |

| 21h         | 80h       | Routing DRDY interrupt to INT2 pin                                                                                |

| 15h         | 03h       | FSR = 4 g and ACTIVE = 1                                                                                          |

#### Observation:

The SDCD block triggers a rising interrupt when the threshold of  $< \pm 100$  mg is met (with debounce of 255 samples).

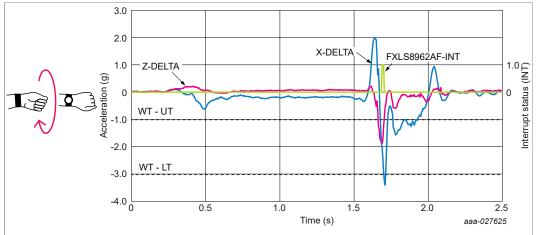

#### 3.3 Twist motion event detection

Example use case: Turn on smartwatch display screen by twisting the hand.

Motion and its signature:

A typical twist motion involves acceleration in any two orthogonal axes. For example, in a smartwatch use case, the two axes in the accelerometer are under motion for a twisting activity as follows:

- · Z- and X-axis showing activity, with the Y-axis remaining relatively stationary

- Z- and Y-axis showing activity, with the X-axis remaining relatively stationary

As shown in <u>Figure 11</u>, when delta values (nth and the initial reference sample) are plotted for the axes, a typical twist motion would show X and Z values having a delta of  $\sim$ -1 g to -3 g from their initial reference position (polarity of thresholds depends on axis orientation and should be determined accordingly).

For a twist activity based smartwatch display application, the suitable reference position would occur when the wrist is facing up and parallel to the ground (where X and Y reads 0 g and Z reads 1 g). Since this reference position is fixed, REF\_UPDM[1:0]=01h is the reference update mode that can be used in the SDCD block.

Figure 11. Twist motion and its signature

Table 9. Register configuration for twist motion event detection

| Register | Value | Description                                                                                                                                              |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15h      | 02h   | FSR = 4 g and Standby mode                                                                                                                               |

| 17h      | 44h   | Wake ODR = 200 Hz and Sleep ODR = 200Hz (Reg 16h = 00h low power mode by default)                                                                        |

| 2Fh      | 05h   | Enable X and Z axis only for SDCD WT function                                                                                                            |

| 30h      | A8h   | Enabling SDCD function, WT logical AND, relative fixed reference mode and set WT Debounce counter to clear immediately when threshold criteria is false. |

| 32h      | 02h   | Debounce time = $2 \times (1/200) = 10$ ms                                                                                                               |

| 33h      | FEh   | Registers 33h and 34h set the OT LOWER threshold. In this case it is set to                                                                              |

| 34h      | F9h   | hex2dec (F9FE) × 1.95 mg/LSB = <b>–3g</b> (1.95 mg/LSB in 4 g mode).                                                                                     |

| 35h      | 00h   | Registers 35h and 36h set the OT UPPER threshold. In this case it is set to                                                                              |

| 36h      | FEh   | hex2dec (FE00) × 1.95 mg/LSB = <b>–1g</b>                                                                                                                |

| 20h      | 90h   | Enabling DRDY_EN and SDCD_WT_EN                                                                                                                          |

| 21h      | 80h   | Routing DRDY interrupt to INT2 pin                                                                                                                       |

| 15h      | 03h   | FSR = 4 g and ACTIVE = 1                                                                                                                                 |

#### **Observation:**

The accelerometer triggers an interrupt every time the WT of  $\sim$ -1 g to  $\sim$ -3 g is met on X and Z axes simultaneously (with debounce time of 10 ms). This interrupt is an indicator of the twist movement of the wrist from a fixed position.

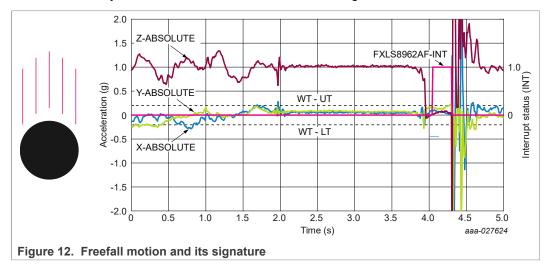

#### 3.4 Freefall motion event detection

Example use case: Human fall detection.

#### Motion and its signature:

A typical freefall event would cause all three axes in the accelerometer to read 0 g as the MEMS in the sensor is subjected to zero acceleration during freefall. Thus to detect a freefall event, a WT event detection can be used in SDCD block. The thresholds can be defined as low as ±200 mg and absolute reference mode shall be used. Since we are expecting a WT event in all three axes during freefall, the WT\_LOG\_SEL bit is set to enable AND logic operation on the axes event flags. Note that debounce time is set to 100 ms to identify the freefall event from a reasonable height.

| Register | Value | Description                                                                                                                                                                       |  |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15h      | 02h   | FSR = 4 g and Standby mode                                                                                                                                                        |  |

| 17h      | 55h   | Wake ODR = 100 Hz and Sleep ODR = 100 Hz                                                                                                                                          |  |

| 2Fh      | 07h   | Enabling SDCD WT for all 3 axes X, Y, Z                                                                                                                                           |  |

| 30h      | E8h   | Enable SDCD function, enable absolute reference mode and set WT logic selection to AND. Debounce behavior is set to clear immediately when threshold criteria evaluates to false. |  |

| 32h      | 0Ah   | Debounce time is 10 samples corresponding to 100 ms                                                                                                                               |  |

| 33h      | 99h   | Registers 33h and 34h set the OT LOWER threshold. In this case it is se                                                                                                           |  |

| 34h      | FFh   | hex2dec (FF99)x1.95 mg/LSB = <b>-200 mg</b> (1.95mg/LSB in 4g mode).                                                                                                              |  |

| 35h      | 67h   | Registers 35h and 36h set the OT UPPER threshold. In this case it is set to                                                                                                       |  |

| 36h      | 00h   | hex2dec (0067)x1.95 mg/LSB = <b>+200 mg</b> (1.95mg/LSB in 4g mode).                                                                                                              |  |

| 20h      | 90h   | Enabling DRDY_EN and SDCD_WT_EN                                                                                                                                                   |  |

| 21h      | 80h   | Routing DRDY interrupt to INT2 pin                                                                                                                                                |  |

| 15h      | 03h   | FSR = 4 g and ACTIVE=1                                                                                                                                                            |  |

#### **Observation:**

The accelerometer triggers a rising interrupt when the WT of <  $\pm 200$  mg is met (with debounce time of 100 ms).

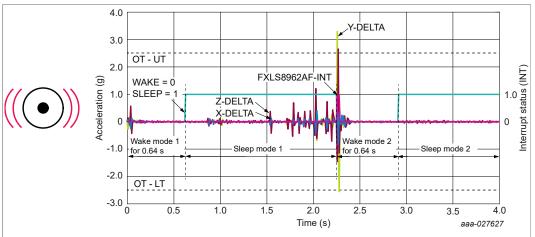

#### 3.5 Transient / tap motion event detection

Example use case: Cycle through the display menu in smartwatch by tapping on it.

#### Motion and its signature:

A typical transient motion involves a sudden jerk exceeding  $\pm 2$  g in any of the X-axis, Y-axis and Z-axis with respect to the previous sample as a reference. Thus, the SDCD reference mode REF\_UPDM[1:0]=10h is used. This allows for acceleration slope detection with Data(n) to Data(n–1) always used as the input to the window comparator.

Note the accelerometer is configured to go into sleep mode when inactive for more than 0.64 seconds and transitions to wake mode on seeing transient activity as observed from the 'WAKE=0/SLEEP=1' trace in Figure 13.

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

Figure 13. Tap event and its signature

| Table 44 | Destates | <b>f</b> !    | f                | · · · · · · · · · · · · · · · · · · · |

|----------|----------|---------------|------------------|---------------------------------------|

|          | Redister | confiduration | tor transient/ta | o event detection                     |

|          |          |               |                  |                                       |

| Register | Value | Description                                                                                                                  |  |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------|--|

| 15h      | 02h   | FSR = 4 g and Standby mode                                                                                                   |  |

| 17h      | 57h   | Wake ODR=100 Hz and Sleep ODR = 25 Hz                                                                                        |  |

| 2Fh      | 38h   | Enabling SDCD OT for all 3 axes X, Y, Z                                                                                      |  |

| 30h      | C0h   | Enabling SDCD and Relative Data (N) – Data (N-1) mode for transient detection                                                |  |

| 31h      | 00h   | Debounce time = 0 for transient detection                                                                                    |  |

| 33h      | FFh   | Registers 33h and 34h set the OT LOWER threshold. In this case it is set to                                                  |  |

| 34h      | FBh   | hex2dec (FBFF) × 1.95 mg/LSB = <b>–2g</b> (1.95 mg/LSB in 4 g mode).                                                         |  |

| 35h      | 01h   | Registers 35h and 36h set the OT UPPER threshold. In this case it is set to hex2dec (0401) $\times$ 1.95 mg/LSB = <b>+2g</b> |  |

| 36h      | 04h   |                                                                                                                              |  |

| 20h      | A0h   | Enabling DRDY_EN and SDCD_OT_EN                                                                                              |  |

| 21h      | 80h   | Routing DRDY interrupt to INT2 pin                                                                                           |  |

| 1Eh      | 40h   | Note: Registers 1Eh and 1Fh enable the ASLP function and set the sleep                                                       |  |

| 1Fh      | 00h   | mode transition timer. In this case it is set to hex2dec (0040) × 10 ms (100 Hz<br>Wake ODR) = <b>0.64 s</b>                 |  |

| 18h      | 21h   | Enable SDCD outside of thresholds event Auto-WAKE/SLEEP transition source enable                                             |  |

| 15h      | 03h   | FSR = 4 g and ACTIVE = 1                                                                                                     |  |

#### **Observation:**

The accelerometer triggers an interrupt every time the WT of >  $\pm 2$  g is met (with debounce time of 10 ms) which in turn transitions the part from sleep to wake mode or prevents part from entering sleep mode.

## Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

### 4 Legal information

### 4.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 4.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Suitability for use in automotive applications — This NXP product has been qualified for use in automotive applications. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 4.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners. **NXP** — wordmark and logo are trademarks of NXP B.V.

Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

### **Tables**

| Tab. 1.<br>Tab. 2. | SDCD programmable threshold registers<br>SDCD programmable timer registers |    |

|--------------------|----------------------------------------------------------------------------|----|

| Tab. 3.            | SDCD_CONFIG2 register                                                      |    |

| Tab. 4.            | SDCD_CONFIG1 register                                                      | 8  |

| Tab. 5.            | Interrupt usage                                                            | 9  |

| Tab. 6.            | SDCD configurations for example use                                        |    |

|                    | cases                                                                      | 12 |

| Tab. 7.            | Register configuration for shake motion event detection                    | 13 |

| Tab. 8.  | Register configuration for motion to no-<br>motion event detection | 14 |

|----------|--------------------------------------------------------------------|----|

| Tab. 9.  | Register configuration for twist motion event detection            | 15 |

| Tab. 10. | Register configuration for freefall event detection                | 17 |

| Tab. 11. | Register configuration for transient/tap event detection           | 18 |

### Figures

| Fig. 1. | Outside-of-thresholds and within-thresholds |   |  |

|---------|---------------------------------------------|---|--|

|         | event                                       | 4 |  |

| Fig. 2. | SDCD functional block diagram               | 4 |  |

| Fig. 3. | Programmable thresholds                     | 5 |  |

| Fig. 4. | Case 1: Debounce behavior set to clear      |   |  |

| Fig. 5. | Case 2: Debounce behavior set to            |   |  |

|         | decrement                                   | 8 |  |

| Fig. 6. | Interrupt latching                          | 9 |  |

| Fig. 7.<br>Fig. 8. | SDCD reference update modes<br>SDCD relative operation mode |    |

|--------------------|-------------------------------------------------------------|----|

| Fig. 9.            | Shake motion and its signature                              |    |

| Fig. 10.           | Motion to no-motion event detection                         |    |

| Fig. 11.           | Twist motion and its signature                              |    |

| Fig. 12.           | Freefall motion and its signature                           |    |

| Fig. 13.           | Tap event and its signature                                 | 18 |

|                    |                                                             |    |

Sensors Data Change Detection (SDCD) block overview with examples for FXLS896xAF and FXLS897xCF accelerometer family

### Contents

| 1   | Introduction                           | 3  |

|-----|----------------------------------------|----|

| 2   | SDCD block                             | 3  |

| 2.1 | Function overview                      | 3  |

| 2.2 | Programmable thresholds                | 5  |

| 2.3 | Programmable debounce counter          | 6  |

| 2.4 | Interrupt logic                        | 8  |

| 2.5 | Reference update modes                 | 10 |

| 3   | Example use cases                      | 12 |

| 3.1 | Shake event detection                  | 12 |

| 3.2 | Motion to no-motion event detection    | 13 |

| 3.3 | Twist motion event detection           | 14 |

| 3.4 | Freefall motion event detection        | 16 |

| 3.5 | Transient / tap motion event detection | 17 |

| 4   | Legal information                      | 19 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 10 March 2023 Document identifier: AN12004